Hold Time (tH): The time interval after the active transition of the clock signal during which the data input (D, J, or K) must be maintained. Setup Time (tS): The time interval before the active transition of the clock signal during which the data input (D, J, or K) must be maintained. Copyright 2009ĭigital Electronics TM 3.1 Introduction to Flip-Flops Flip-Flop Timing Data Input (D,J, or K) 1 tS Setup Time tH Hold Time Positive Edge Clock Definition of the Setup & Hold Time timing parameters for a flip-flop.

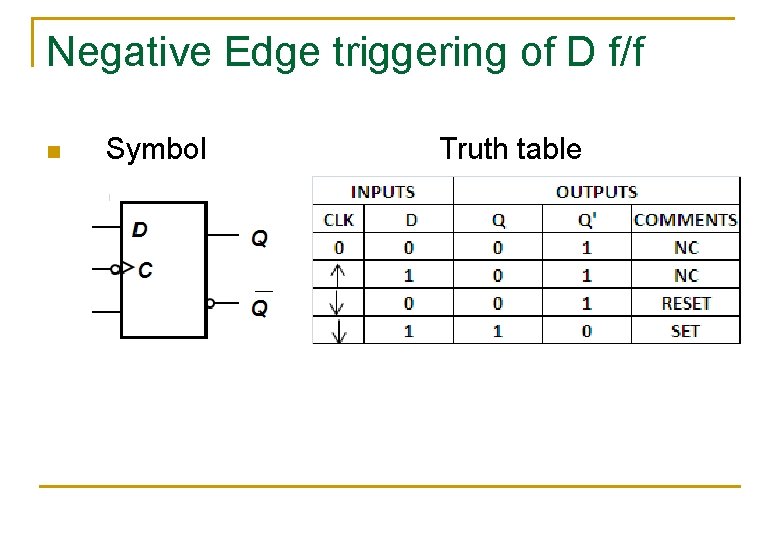

Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops POS & NEG Edge Triggered J/K Positive Edge Trigger K J Q CLK J K CLK 1 : Rising Edge of Clock Negative Edge Trigger Schematic symbol and excitation table for the positive edge triggered and negative edge triggered J/K flip-flops K J Q CLK J K CLK 1 : Rising Edge of Clock Project Lead The Way, Inc. Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops POS & NEG Edge Triggered D Positive Edge Trigger CLK D Q D CLK 1 : Rising Edge of Clock Negative Edge Trigger Schematic symbol and excitation table for the positive edge triggered and negative edge triggered D flip-flops CLK D Q D CLK 1 : Falling Edge of Clock Project Lead The Way, Inc. Copyright 2009ĭigital Electronics TM 3.1 Introduction to Flip-Flops Clock Edges Positive Edge Transition 1 Negative Edge Transition Project Lead The Way, Inc. Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops J/K Flip-Flop: Example Timing NO CHANGE NO CHANGE SET TOGGLE TOGGLE CLEAR SET Q J K CLK Timing diagram example for a J/K flip-flop. Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops J/K Flip-Flop: Excitation Table K J Q CLK J K CLK No Change 1 Clear Set Toggle : Rising Edge of Clock Schematic symbol and excitation table for the J/K flip-flop. Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops D Flip-Flop: Example Timing Q=D=1 Q=D=0 Q=D=0 No Change Q=D=1 Q=D=1 No Change Q=D=0 Q=D=0 No Change Q D CLK Timing diagram example for a D flip-flop. Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops D Flip-Flop: Excitation Table CLK D Q D CLK 1 : Rising Edge of Clock Schematic symbol and excitation table for the D flip-flop. Thus, sequential logic requires memory to store these previous outputs values. However, the outputs are a function of both the present value of the inputs and also the previous output values. Sequential logic can have one or more, inputs and one or more outputs. Inputs Outputs Memory Elements (Flip-Flops) Clock Definition of sequential logic. Copyright 2009įlip-FLops and Latches Digital Electronics TM 3.1 Introduction to Flip-Flops Sequential Logic & The Flip-Flop Combinational Logic Gates. Introductory Slide / Overview of Presentation Project Lead The Way, Inc. Introduce the J/K flip-flop and provide an excitation table and a sample timing analysis. Introduce the D flip-flop and provide an excitation table and a sample timing analysis. Copyright 2009ĭigital Electronics TM 3.1 Introduction to Flip-Flops Flip-Flops & Latches This presentation will Review sequential logic and the flip-flop. Presentation on theme: "Flip-FLops and Latches"- Presentation transcript:ĭigital Electronics TM 3.1 Introduction to Flip-Flop Flip-Flops & Latches Project Lead The Way, Inc.

0 kommentar(er)

0 kommentar(er)